| EDA实验课课程笔记(七) | 您所在的位置:网站首页 › 用于逻辑综合的vhdl pdf › EDA实验课课程笔记(七) |

EDA实验课课程笔记(七)

|

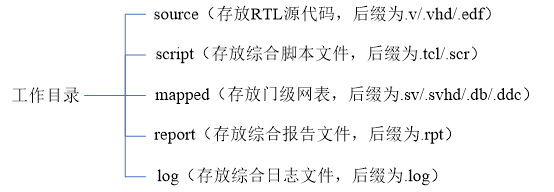

本博文用于记录DC的基本知识及一些相关的最基本概念。然后配合演示视频,对DC有一个最初步的认识。参考学校老师的PPT讲解,以及实验指导书中的内容。 Design Compiler的简介及其图像化使用 0,前言(1)数字IC的设计流程(2)综合(3)逻辑综合的工具 1,DC的简介(1)主要目标及其综合步骤(2)DC相关概念1)启动文件2)系统库变量3)工作目录4)设计对象5)设计约束文件SDC (3)时序分析相关概念1)建立时间与保持时间2)传播延时3)时间路径4)时序弧5)输入延时6)输出延时7)裕度8)关键路径9)最差时间违反10)总的时间违反11)伪路径12)多周期路径 3,DC图形化操作演示视频 0,前言 (1)数字IC的设计流程项目需求:芯片的设计指标 系统级设计:系统语言进行建模 前段设计:RTL设计,RTL仿真,硬件原型验证(FPGA上进行验证),电路综合 后端设计:版图设计,物理验证,后仿真等 数字系统可以在多个层次上进行描述,将较高层次的描述转化为较低层次的描述过程就是综合。综合分为三个层次: 高层次综合(High-Level Synthesis):负责将系统算法层的行为描述转化为寄存器传输层的结构描述;例如X家的HLS。逻辑综合(Logic Synthesis):负责将寄存器传输层的结构描述转化为逻辑层的结构描述,以及将逻辑层的结构描述转化为电路的结构描述;得到门与门的连接关系。–本课程学习版图综合(Layout Synthesis)负责将系统电路层的结构描述转化为版图层的物理描述;–模拟集电路学习 (3)逻辑综合的工具 美国Synopsys公司的Design Compiler;美国Cadence DesignSystems公司的PKS和BuildGates;美国MAGMA公司的Blast RTL;美国Synplicity公司的Synplify和Amplify;逻辑综合的过程是约束驱动、路径驱动和模板驱动 约束驱动指EDA工具根据设计人员对电路提出的时序和面积等目标要求进行工作路径驱动指EDA工具采用静态时序分析方法计算设计中各条路径的时序模板驱动指设计人员编写的代码要能被EDA工具理解和接受 1,DC的简介DC主要就是将RTL级转换为网表级 (1)主要目标及其综合步骤主要学习约束信息的添加以及修正RTL代码的书写风格 启动文件用来指定综合工具所需要的一些初始化信息。DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: • DC安装目录($DC_PATH/admin/setup) • 用户主目录 • 工具启动目录 • 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

DC中分为8种类型: 设计(Design) :一种能完成一定逻辑功能的电路,可以是独立的,也可以是层次化的设计。(当前设计)单元(Cell):设计中包含的子设计的实例,也称为instance。参考(Reference) :所指向的设计原型,即单元是参考的实例。端口(Port):设计的基本输入、输出和双向的输入输出。引脚(Pin):单元的输入输出和双向的输入输出。线网(Net):端口和引脚间及引脚和引脚间的连线。时钟(Clock):作为时钟信号源的引脚或端口。库(Library):直接与工艺相关的一组单元的集合,是生成门级网表的基本单元或设计中被实例化的单元。 5)设计约束文件SDC

5)设计约束文件SDC

SDC-Synopsys Design Constraint 提供简单而又直接的方法来设定设计目标,包括时序、面积、功耗和设计规则约束等全部约束信息。 SDC文件由TCL格式的约束命令组成,既可以由设计者手动编写,也可以由工具生成,一般后者是主要的生成方式。

时钟到输出的时间:指从时钟触发开始到寄存器输出端获得有效稳定数据所经历的时间,也称为寄存器的传播延时(Tco) (或污染延时) 时间路径:信号传播经过的逻辑通道,简称路径。DC的时序分析是基于路径的。DC的时序分析引擎DesignTime将设计划分成一系列的信号通路。然后对这些路径进行分析 起点一般为:基本输入端口或寄存器的时钟端口; 终点一般为:基本输出端口或寄存器的数据端口。 时间路径通常分为4种: 基本输入到基本输出:PATH 2 基本输入到寄存器: PATH 1 寄存器到基本输出:PATH 4 寄存器到寄存器:PATH 3 时序弧(timing arc):指路径延时的最小组成部分。 DesignTime将每条时序路径划分成一条条称为时序弧(有些资料也成为延时段)的连线延时或单元延时来计算总的路径延时。

裕度(slack):是时序要求与实际时序之间的差值,反映了时序是否满足要求。裕度为正,满足要求;反之不满足。 裕度=要求的时间-实际的时间 8)关键路径关键路径:指设计中违反时间约束或时间容限很小(刚刚满足设计约束)的路径。这些是优化的重点。 9)最差时间违反• 最差时间违反(worst negative slack):指一个信号从路径起点到终点所需时间超过约束最严重的情况。 10)总的时间违反• 总的时间违反(total negative slack):指每个路径终点对应的最差时间违反之和。 11)伪路径• 伪路径:也称为虚假路径、无效路径或异步路径,指时序分析器不能对其进行正确分析的路径,比如不同时钟域之间的过渡路径、复位信号的作用域等,这些路径上出现的时序违规实际是假违规。 12)多周期路径• 多周期路径:指延时超过1个时钟周期的路径。 • 综合时明确指出伪路径和多周期路径,DC就会更有效地优化其他关键路径,而不是花费大量时间和性能去优化假的违规。 3,DC图形化操作演示视频点我看视频 EDA实验简要记录 |

【本文地址】

• DC提出的逻辑综合步骤是:逻辑综合=翻译+优化+映射 • 翻译:将HDL代码转换成GTECH库(Synopsys提供的独立于工艺的元件库)中单元表示的网表; • 优化:与工艺无关的阶段,运用布尔变换或代数变换技术来优化逻辑,包括结构优化、逻辑优化和门级优化 ; • 映射:将GTECH库元件映射到某一特定的半导体工艺库上,此时的电路网表包含了相关的工艺参数。 优化和映射是同时进行的,没有执行步骤上的先后,因此综合是一个迭代过程。

• DC提出的逻辑综合步骤是:逻辑综合=翻译+优化+映射 • 翻译:将HDL代码转换成GTECH库(Synopsys提供的独立于工艺的元件库)中单元表示的网表; • 优化:与工艺无关的阶段,运用布尔变换或代数变换技术来优化逻辑,包括结构优化、逻辑优化和门级优化 ; • 映射:将GTECH库元件映射到某一特定的半导体工艺库上,此时的电路网表包含了相关的工艺参数。 优化和映射是同时进行的,没有执行步骤上的先后,因此综合是一个迭代过程。

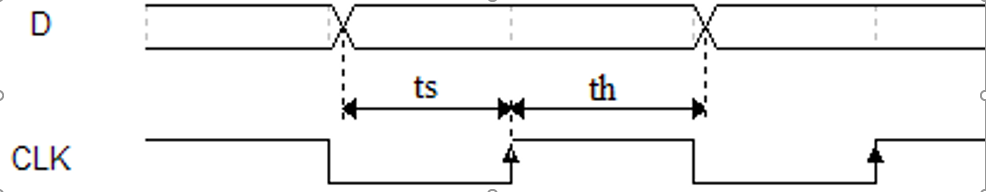

建立时间(ts):指寄存器的时钟信号有效沿到来之前数据必须稳定的最小时间。 保持时间(th):指寄存器的时钟信号有效沿到来之后数据必须稳定的最小时间。

建立时间(ts):指寄存器的时钟信号有效沿到来之前数据必须稳定的最小时间。 保持时间(th):指寄存器的时钟信号有效沿到来之后数据必须稳定的最小时间。